Binnenin de processor: zo ontstaan computerchips

Stap 6: Ionen-bombardement

In deze stap worden de geleidende eigenschappen van het silicium gewijzigd. Men kan p-type of n-type materiaal maken en kan het meer of minder geleidend maken. Dit gebeurt door het silicium te bombarderen met ionen van een ander materiaal. De ionen nestelen zich in de ontblote delen van de wafer: de bronnen en de afvoeren van de transistors (groen). Voor sommige ionen zoals Fosfor (P) of Arseen (As) wordt het een n-mos-transistor, andere ionen zoals Boor (B) zorgen voor een p-mos-transistor. Visueel zien beiden er hetzelfde uit, maar de elektrische eigenschappen verschillen. Zoals gezegd laat de n-mos-transistor enkel stroom door wanneer de poort op een positieve spanning staat t.o.v de bron. De p-mos laat stroom door van bron naar afvoer voor negatieve spanningen op de poort. De ionen versmelten in essentie met het silicium-monokristal en geven het zo andere elektrische eigenschappen. Hoe meer ionen er geïmplanteerd worden, hoe meer geleidend de halfgeleider wordt. Dat gaat niet met alle materialen; je hebt er een halfgeleider voor nodig.

De stappen in het fabricageproces zijn erg chemisch. Materialen reageren met elkaar en dat gaat beter als het warm is. De meeste stappen gebeuren daarom op hoge temperatuur, tot wel 800 of zelfs 1000 graden Celsius. Dat verklaart meteen waarom chips ‘gebakken’ worden.

Woestijn

Een eenvoudige, zij het ietwat grove visualisatie helpt misschien: zie de wafer in deze fase als een immense woestijn. De oxidelaag is woestijngras. De hele woestijn is gevuld met miljarden barre rechthoeken waar geen gras groeit, maar je enkel zand ziet. Die rechthoeken raken elkaar nooit: stukken met gras belemmeren dat. De zanderige vakken zijn in twee gesplitst door een dikke balk: de transistorpoort. Tot slot passeren er twee zandstormen. De ene heeft erg donker zand bij. Dat mengt zich met de bovenste laag van enkele blootgestelde vierkanten. Zij worden p-mos-transistors. De tweede zandstorm met lichter zand treft de andere vierkanten. Die noemen we nu n-mos-transistors. Het resultaat: een woestijn met veel woestijngras en daarin miljarden barre vakjes, sommigen met licht zand, sommigen met donker zand, allemaal met een balk die hen doormidden splitst.

In werkelijkheid is het productieproces aanzienlijk ingewikkelder dan wat we hierboven beschrijven. Er komen meer materialen aan te pas, maar het principe is telkens hetzelfde: de hele wafer wordt bedekt, lithografie zorgt voor een patroon van beschermend fotoresist en zuur of gas etst onbeschermde delen weg, totdat de gewenste constructies overblijven.

Kleiner dan klein

Intel bakt z’n Skylake- en Broadwellchips op 14 nanometer, maar dat wil niet zeggen dat de transistors maar 14 nanometer groot zijn. De 14 nanometer is in dit geval een vrij belangrijk, maar niet noodzakelijk nauwkeurig, getal dat weergeeft wat het gemiddelde formaat van een constructie (poort, bron, afvoer…) op de chip is. Sommige delen zijn iets kleiner dan 14 nm, andere groter.

Na het ionenbombardement en opeenvolgingen van het deponeren van materiaal, lithografie en etsen zijn de transistors klaar.

Ze worden vrijwel helemaal bedekt door een isolerend materiaal, op drie contactpunten (rood) na: de bron, de poort en de afvoer krijgen zo’n metalen contactje mee.

De Wet van Moore, intussen geschiedenis, voorspelde een halve eeuw lang het verloop van de ontwikkeling van de computerchip. Moore voorspelde terecht een verdubbeling van het aantal transistors op een geïntegreerde schakeling (van eenzelfde formaat), en dat iedere twee jaar. Meer transistors op eenzelfde plaats betekent een verkleining van die transistors. Het binnenwerk van computerchips wordt dus steeds kleiner, maar het productieproces steeds moeilijker.

Waarom maakt het formaat van een transistor nu zoveel uit? Hoe zorgen die transistors er voor dat jouw computer Windows kan draaien? En hoe moeilijk is het om een hedendaagse computerchip te maken? We zochten het uit, van het zand tot de Core i7 in je laptop en alles daartussen.

Stap 1: De wafer

Zand: erg high-tech kan je het voornaamste element van de computerchip niet noemen. Zand, in de vorm van verfijnd silicium, vormt de basis van de computerchip. Dat silicium wordt gepurificeerd en vervolgens gesmolten. Door het silicium langzaam te laten stollen, ontstaat er een cilindervormig monokristal. Een dergelijk kristal heeft een uniforme structuur van silicium-atomen, waardoor het als basis van een computerchip kan dienen. Silicium is een halfgeleider en heeft zo de essentiële eigenschappen voor het maken van transistors. Waarom dat belangrijk is, dat lees je verder.

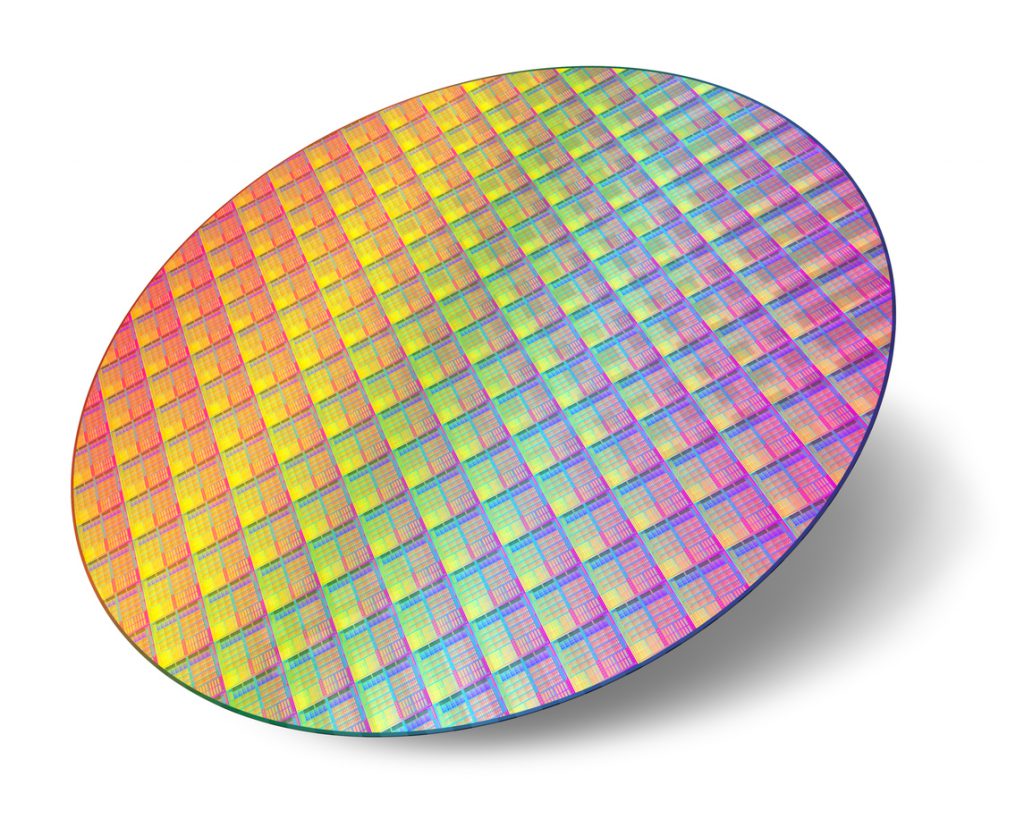

Uit het cilindervormige blok siliciumkristal, dat een slordige 100 kilo weegt, worden nu schijven gesneden van 300 millimeter diameter en 1 millimeter dik: de wafer. De wafer is de fundering van de microchip, of het nu gaat om een 14 nm Skylake-chip van Intel, of een ouderwetse rekenchip in je Ti83+ grafische rekenmachine van Texas Intruments.

De wafer wordt gemaakt door een toeleverancier en gaat vervolgens de bakkerij in. Dat kan bij het Leuvense imec zijn, waar onderzoek wordt gedaan op het scherpst van de snee om de computerchip van morgen te ontwikkelen. Of in een fabriek van een fabrikant zoals Intel of GlobalFoundries, waar de productie van de chips in je laptop begint. Er bestaan heel wat fabrieken waar men computerchips maakt, maar slechts weinig computerbouwers hebben zelf een dergelijke installatie. Intel en Samsung hebben de productie van hun eigen processors in handen, maar de meeste fabrikanten besteden het maken van een microchip uit aan derden, zoals bijvoorbeeld GlobalFoundries, waar AMD mee samenwerkt, TSMC, of Samsung dat ook z’n eigen fabrieken heeft.

In een chipfabriek, kortweg fab genoemd, ondergaat de wafer honderden fabricagestappen waarin de microchip als het ware laag op laag gegroeid wordt op de silicium-fundering. Dat proces begint met het maken van de transistors: het belangrijkste element van de chip.

De elementaire bouwsteen

Alle transistors in microchips zijn Mosfets. Mosfet, wat staat voor metal-oxide-semiconductor field-effect transistor, is de basisbouwsteen van de hele digitale revolutie en maakt tot vandaag mogelijk dat een microchip überhaupt kan bestaan.

Een transistor is in essentie een schakelaar. De dingen bestaan uit een bron, een poort en een afvoer. Stroom loopt via de bron naar de afvoer, maar alleen wanneer de poort dat toestaat. Is de poort gesloten, dan vloeit er geen stroom door de transistor. Er bestaan twee soorten microtransistors: p-mos en n-mos-transistors. De p-mos-transistor laat enkel stroom door wanneer een negatieve spanning aan de poort wordt aangelegd. De n-mos-transistor werkt omgekeerd: de poort is open wanneer een positieve spanning wordt aangelegd.

Samen slim

Doordat de p-mos-transistor en de n-mos-transistor omgekeerd reageren op een elektrische spanning, kan je ze combineren tot slimme schakelingen. Een circuit dat p-mos- en n-mos-transistors combineert, noemen we een CMOS-circuit.

“Alle microchips ter wereld maken gebruik van CMOS”, verduidelijkt Guido Groeseneken, fellow bij imec en professor aan de KU Leuven. Hij helpt ons wegwijs te raken doorheen de binnenkant van de microchip. “Zonder CMOS kan een kleine chip niet bestaan.” Warmte wordt dan een onoverkoombaar probleem. Groeseneken: “Ook met één soort transistor (p-mos of n-mos) is het mogelijk om een slimme schakeling te bouwen, maar door een dergelijke schakeling loopt de helft van de tijd stroom naar de aarding.” Schakelingen met enkele miljoenen of een miljard transistors samen zouden dan voor honderden ampères stroom zorgen. De hitte die dat met zich meebrengt, is onmogelijk te beheersen. “Door een CMOS-schakeling loopt nauwelijks stroom, of de output nu 1 of 0 is, althans in statische toestand. Zelfs met miljarden transistors op één chip gaat het dan slechts om enkele ampères.” De chip moet nog steeds gekoeld worden, maar dezer dagen kan dat zelfs passief, zoals de nieuwste laptops zonder ventilator aantonen.

Een computerchip bestaat uit tientallen lagen, maar alle transistors bevinden zich op de onderste laag, op het silicium van de wafer. De miljarden transistors worden niet individueel geplaatst, een combinatie van chemische processen zorgt ervoor dat ze geleidelijk ontstaan. In een fab ondergaat een wafer een opeenvolging van vier basisstappen: het deponeren van materiaal, de lithografie, het etsen en de ionen-implantatie.

| Inhoudsopgave | |

| Stap 1: De wafer | Stap 6: Ionen-bombardement |

| Stap 2: Eerste laagje | Stap 7: Verbindingen |

| Stap 3: Lithografie | Het gereedschap |

| Stap 4: Etsen | De afwerking |

| Stap 5: De poort |

Stap 2: Eerste laagje

Het maken van een nanotransistor is een abstract proces. Het gekleurde schema Op de vorige pagina toont een afgewerkte transistor en kan helpen bij het visualiseren. Doorheen de tekst bouwen we het schema stap voor stap op.

Alles begint met het deponeren van een materiaal op de wafer. Dat materiaal wordt uniform over de hele wafer verspreid. Het eerste materiaal dat gedeponeerd wordt bovenop het silicium, is een oxide (lichtblauw). Dat oxide bedekt nu het silicium van de wafer (grijs). Om de transistors te maken, moeten er echter delen van de wafer vrij zijn van oxide, zodat het silicium weer komt piepen.

Dat gebeurt door delen van het materiaal weg te etsen. Dat etsen is een chemisch proces: een zuur of een gas wordt losgelaten op de wafer, waarna het oxide verdwijnt. Het is niet mogelijk om slechts bepaalde delen van de wafer aan te tasten en andere te vrijwaren. De oplossing: delen van het oxide beschermen tegen het zuur of het gas, zodat ze niet worden weggevreten.

| Inhoudsopgave | |

| Stap 1: De wafer | Stap 6: Ionen-bombardement |

| Stap 2: Eerste laagje | Stap 7: Verbindingen |

| Stap 3: Lithografie | Het gereedschap |

| Stap 4: Etsen | De afwerking |

| Stap 5: De poort |

Stap 3: Lithografie

De beschermingslaag wordt toegevoegd in de lithografiestap. Het principe achter lithografie is doodeenvoudig. Je kent het vanuit de fotografie, voor die digitaal werd. Een laagje lichtgevoelig materiaal, fotoresist genoemd, wordt ergens gedeponeerd, licht schijnt op specifieke delen van dat materiaal en er ontstaan patronen. In de fab krijgt de ganse wafer een laag fotogevoelig materiaal over zich heen. Vervolgens worden delen van dat materiaal belicht doorheen een zogenaamd masker. De stukken die licht op zich krijgen, blijven vloeibaar en kunnen eenvoudig weggewassen worden. De niet-belichte delen verharden (andersom kan ook, al naargelang het type fotoresist.) Groeseneken: “Een masker bepaalt welke delen van de wafer belicht worden”. Een masker is een patroon, een soort blauwdruk of stencil zeg maar, dat tussen de lichtbron en de wafer geplaatst wordt. Met de hulp van dat patroon is het mogelijk om heel nauwkeurig specifieke delen te belichten, tot op het nanometerniveau.

Na de lithografie-stap is de wafer op bepaalde delen bedekt en beschermd door het verharde, lichtgevoelige materiaal. Het niet-verharde fotoresist wordt weggewassen, waardoor stukken van de chip in wording bloot komen te liggen. In deze eerste stap in het maken van een microchip is de oxidelaag bovenop het silicium overal beschermd door verhard fotoresist, behalve op de plaatsen waar de transistors komen. Daar werd het fotoresist niet bestraald en werd het weggewassen.

| Inhoudsopgave | |

| Stap 1: De wafer | Stap 6: Ionen-bombardement |

| Stap 2: Eerste laagje | Stap 7: Verbindingen |

| Stap 3: Lithografie | Het gereedschap |

| Stap 4: Etsen | De afwerking |

| Stap 5: De poort |

Stap 4: Etsen

Vervolgens ondergaat de wafer een andere stap zoals in dit geval het etsen met de hulp van een zuur of een gas. Tijdens het etsen, verdwijnt het oxide op de niet-beschermde plaatsen, zodat daar het silicium van de wafer opnieuw bloot komt te liggen. Na het weghalen van het verharde fotoresist, dat zijn job heeft gedaan, blijft er op de wafer een oxidepatroon over dat perfect het ontwerp van het masker volgt.

In deze eerste stap wordt lithografie gebruikt om stukken van de wafer te bedekken met het oxide, terwijl andere stukken vrij blijven, maar gedurende het hele fabricageproces blijft het principe hetzelfde. De ‘vakjes’ silicium die nu blootliggen, vormen de basis van de transistors. De vakjes zullen binnenkort met de hulp van een ionenbombardement specifieke eigenschappen krijgen. Sommige worden zo p-mos-transistors, terwijl andere n-mos-transistors worden, maar daar zijn we nog niet. Je weet intussen dat een transistor uit een bron, een poort en een afvoer bestaat. De vakjes bloot silicium moeten nu in twee gesplitst worden. Dat gebeurt door het deponeren van een nieuw materiaal, geen oxide, maar een andere stof. Die stof komt als een balkje netjes in het midden van de vakjes bloot silicium terecht. Het balkje wordt de poort van de transistor (donkerblauw), één kant van het blote silicium wordt de bron, de andere kant de afvoer.

| Inhoudsopgave | |

| Stap 1: De wafer | Stap 6: Ionen-bombardement |

| Stap 2: Eerste laagje | Stap 7: Verbindingen |

| Stap 3: Lithografie | Het gereedschap |

| Stap 4: Etsen | De afwerking |

| Stap 5: De poort |

Stap 5: De poort

Ook deze balkjes worden niet secuur gelegd: opnieuw wordt de hele chip bedekt in het balkjesmateriaal, waarna door middel van lithografie de balkjes zelf beschermd worden door het fotoresist en de rest wordt weggeëtst. “Een wafer ondergaat zo tientallen lithografiestappen”, verduidelijkt Groeseneken. “Iedere stap heeft een andere functie, zoals het bouwen van de poort van de transistor, of het toevoegen van isolerend materiaal tussen de transistors. Telkens een wafer een nieuwe lithografiestap ondergaat, wordt daar een nieuw masker voor gebruikt.” Logisch, aangezien het telkens andere delen zijn die beschermd moeten worden.

Een nieuwe ets-stap vreet dus het onbeschermde poortmateriaal weg, waarna alleen de poort overblijft. De chip bestaat op dit moment uit miljarden vakjes silicium met daarboven een poort. Tijd voor de ionenimplantatie.

| Inhoudsopgave | |

| Stap 1: De wafer | Stap 6: Ionen-bombardement |

| Stap 2: Eerste laagje | Stap 7: Verbindingen |

| Stap 3: Lithografie | Het gereedschap |

| Stap 4: Etsen | De afwerking |

| Stap 5: De poort |

Stap 6: Ionen-bombardement

In deze stap worden de geleidende eigenschappen van het silicium gewijzigd. Men kan p-type of n-type materiaal maken en kan het meer of minder geleidend maken. Dit gebeurt door het silicium te bombarderen met ionen van een ander materiaal. De ionen nestelen zich in de ontblote delen van de wafer: de bronnen en de afvoeren van de transistors (groen). Voor sommige ionen zoals Fosfor (P) of Arseen (As) wordt het een n-mos-transistor, andere ionen zoals Boor (B) zorgen voor een p-mos-transistor. Visueel zien beiden er hetzelfde uit, maar de elektrische eigenschappen verschillen. Zoals gezegd laat de n-mos-transistor enkel stroom door wanneer de poort op een positieve spanning staat t.o.v de bron. De p-mos laat stroom door van bron naar afvoer voor negatieve spanningen op de poort. De ionen versmelten in essentie met het silicium-monokristal en geven het zo andere elektrische eigenschappen. Hoe meer ionen er geïmplanteerd worden, hoe meer geleidend de halfgeleider wordt. Dat gaat niet met alle materialen; je hebt er een halfgeleider voor nodig.

De stappen in het fabricageproces zijn erg chemisch. Materialen reageren met elkaar en dat gaat beter als het warm is. De meeste stappen gebeuren daarom op hoge temperatuur, tot wel 800 of zelfs 1000 graden Celsius. Dat verklaart meteen waarom chips ‘gebakken’ worden.

Woestijn

Een eenvoudige, zij het ietwat grove visualisatie helpt misschien: zie de wafer in deze fase als een immense woestijn. De oxidelaag is woestijngras. De hele woestijn is gevuld met miljarden barre rechthoeken waar geen gras groeit, maar je enkel zand ziet. Die rechthoeken raken elkaar nooit: stukken met gras belemmeren dat. De zanderige vakken zijn in twee gesplitst door een dikke balk: de transistorpoort. Tot slot passeren er twee zandstormen. De ene heeft erg donker zand bij. Dat mengt zich met de bovenste laag van enkele blootgestelde vierkanten. Zij worden p-mos-transistors. De tweede zandstorm met lichter zand treft de andere vierkanten. Die noemen we nu n-mos-transistors. Het resultaat: een woestijn met veel woestijngras en daarin miljarden barre vakjes, sommigen met licht zand, sommigen met donker zand, allemaal met een balk die hen doormidden splitst.

In werkelijkheid is het productieproces aanzienlijk ingewikkelder dan wat we hierboven beschrijven. Er komen meer materialen aan te pas, maar het principe is telkens hetzelfde: de hele wafer wordt bedekt, lithografie zorgt voor een patroon van beschermend fotoresist en zuur of gas etst onbeschermde delen weg, totdat de gewenste constructies overblijven.

Kleiner dan klein

Intel bakt z’n Skylake- en Broadwellchips op 14 nanometer, maar dat wil niet zeggen dat de transistors maar 14 nanometer groot zijn. De 14 nanometer is in dit geval een vrij belangrijk, maar niet noodzakelijk nauwkeurig, getal dat weergeeft wat het gemiddelde formaat van een constructie (poort, bron, afvoer…) op de chip is. Sommige delen zijn iets kleiner dan 14 nm, andere groter.

Na het ionenbombardement en opeenvolgingen van het deponeren van materiaal, lithografie en etsen zijn de transistors klaar.

Ze worden vrijwel helemaal bedekt door een isolerend materiaal, op drie contactpunten (rood) na: de bron, de poort en de afvoer krijgen zo’n metalen contactje mee.

| Inhoudsopgave | |

| Stap 1: De wafer | Stap 6: Ionen-bombardement |

| Stap 2: Eerste laagje | Stap 7: Verbindingen |

| Stap 3: Lithografie | Het gereedschap |

| Stap 4: Etsen | De afwerking |

| Stap 5: De poort |

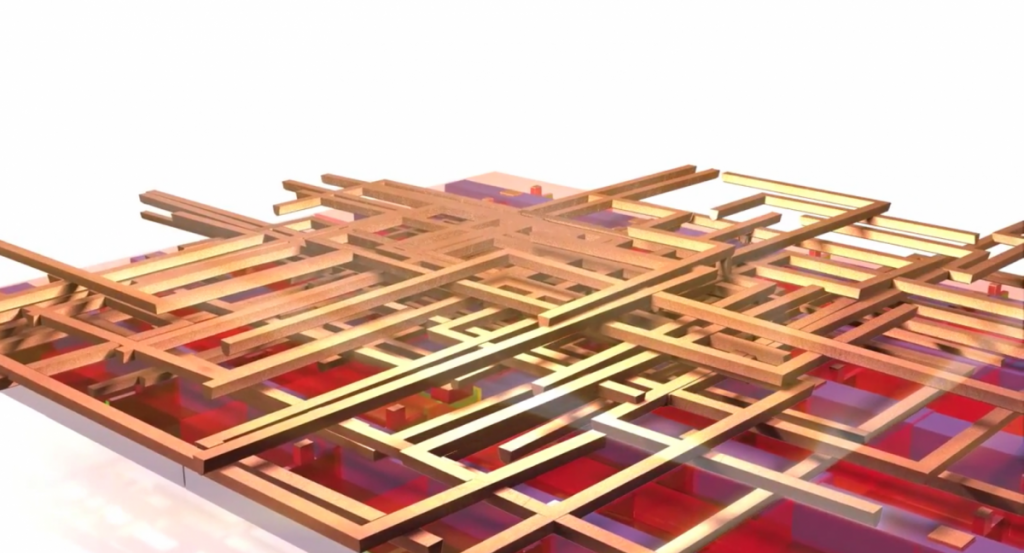

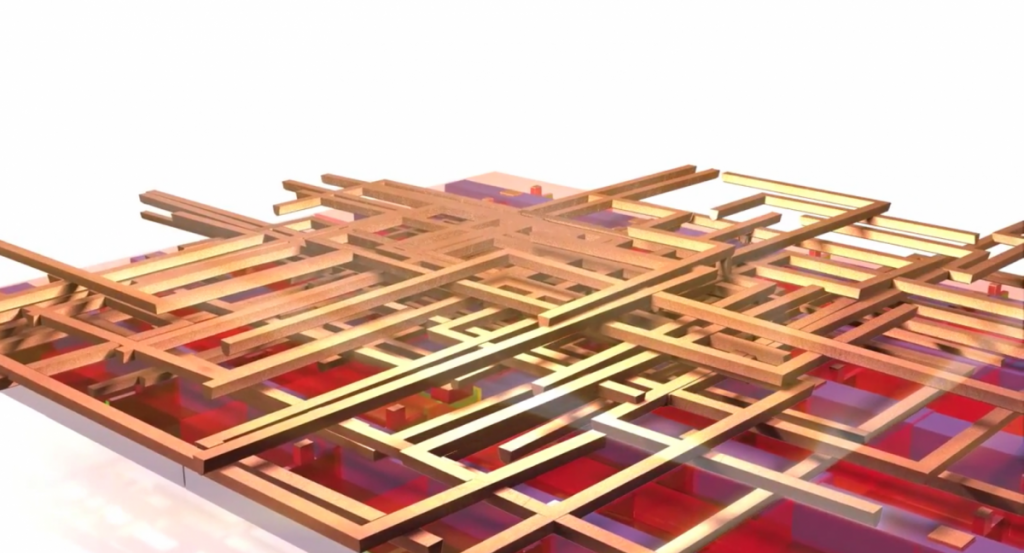

Stap 7: Verbindingen

Na het maken van de transistors en de contacten, worden de verbindingen gelegd. Zowel de poort als de bron en de afvoer worden verbonden met andere bronnen, poorten of afvoeren via kleine verbindingen, meestal vervaardigd uit koper. Die zogenaamde interconnects verbinden contactpunten met elkaar zodat logische schakelingen ontstaan. Ook de interconnects worden laag per laag opgebouwd, naar analogie met de transistor. In dit geval worden in een isolerende laag gleuven geëtst, die nadien wordt opgevuld met koper. Het overtollige koper wordt dan weggepolijst. Het resultaat: één laag van koper interconnects ingebed in een isolerende laag. Zo worden er verschillende interconnectlagen boven mekaar gestapeld, die onderling verbonden worden door zogenaamden via’s. De verbindingen het dichtst bij de transistor zijn piepklein: rond de tien nanometer. Hoe hoger de laag, hoe breder de interconnects worden. Groeseneken trekt de analogie met het wegennet. “De grote interconnects zijn als de autosnelwegen. Zij krijgen grotere hoeveelheden stroom te verwerken. Ze vertakken in steeds kleiner wordende interconnects voor het vormen van de logische schakelingen, tot aan de kleinste interconnects waarmee de transistors verbonden worden, net zoals de woonwijken verbonden worden door een dicht netwerk van kleinere straten.

Architecten

Welke transistors verbonden worden en op welke manier, dat is het werk van de chip-architect. Die bedenkt de combinatie van logische schakelingen die een processor in staat stelt complexe taken uit te voeren en softwarecode te draaien. “Hij wordt daarbij geholpen door software”, weet Groeseneken. “De architect bedenkt wat de chip precies moet doen en de software vertaalt dat naar specifieke verbindingen.” Die verbindingen worden dan opgedeeld in lagen, iedere laag krijgt een masker, en het bouwproces kan beginnen.

Dat klinkt misschien niet eenvoudig, maar het productieproces is nog moeilijker dan je denkt. Héél erg kort door de bocht is de lithografie het potlood waarmee materialen op nanometerniveau getekend en weggegomd worden in de juiste patronen. Een machine die instaat voor de lithografie van bijvoorbeeld Intels 14 nanometerchips moet nauwkeurig zijn tot op twee nanometer. Ter illustratie: al naargelang de bron (en de persoon) groeit het haar op je hoofd met 1 tot acht nanometer per seconde.

| Inhoudsopgave | |

| Stap 1: De wafer | Stap 6: Ionen-bombardement |

| Stap 2: Eerste laagje | Stap 7: Verbindingen |

| Stap 3: Lithografie | Het gereedschap |

| Stap 4: Etsen | De afwerking |

| Stap 5: De poort |

Het gereedschap

Lithografiemachines zijn de duurste toestellen die je terugvindt in een fab. Zoals bij alle dure nicheproducten is er niet al te veel ruimte voor concurrentie in de fabricage ervan. Meer dan 80 procent van ’s werelds lithografiemachines zijn van de hand van ASML, een bedrijf met hoofdkwartier in Veldhoven in Nederland. Rijd je met de wagen van Turnhout naar Eindhoven, dan zie je de campus van het bedrijf met duidelijk zichtbare toren op de linkerkant. Daar liggen kantoor- en onderzoeksgebouwen, maar ook assemblagehallen. Wij wandelden rond in de fabriek, maar niet alvorens we onze cleansuit aantrokken.

Logisch: stof bestaat voornamelijk uit menselijke huidcellen. Jij en ik zijn dus stofproducenten eersteklas. Een enkel stofje binnenin een ASML-machine die wafers behandelt, kan een hele wafer om zeep helpen. Het pak moet in een specifieke volgorde worden aangetrokken, zodat je de fabriek binnenwandelt in een kostuum dat nergens de vuile grond heeft aangeraakt. Ons aangezicht bleef wel vrij, wat betekende dat we niet in de meest gevoelige plaatsen van de fabriek mochten komen. “Dit productieproces helemaal stofvrij houden is onmogelijk”, vertelt Jos Vreeker van ASML. “Hoe proper onze cleanroom ook is, in de fabs van onze klanten gaat het er nog veel strakker aan toe.” Tijdens het productieproces worden wafers zoveel mogelijk in een vacuüm gehouden en zijn er plaatsen waar technici alleen komen in nog specialere pakken, voorzien van een gasmasker en een luchtfles.

Prijzig

ASML maakt machines voor verschillende klanten, die niet allemaal nood hebben aan ’s werelds kleinste of meest geavanceerde chips. Hoe geavanceerder de machine en hoe kleiner de structuren op de chip die belicht dienen te worden, hoe groter het toestel. “De prijs verschilt al naargelang het type, maar een geavanceerd systeem kost gemiddeld 50 tot 70 miljoen euro”, vertrouwt Vreeker ons toe. “Ons meest geavanceerde systeem kost zelfs 100 miljoen euro” De snelste machine van ASML behandelt zo’n 257 wafers per uur. Dat wil niet zeggen dat er 275 wafers met afgewerkte chips uit het toestel komen: lithografie is slechts één stap in het productieproces, die bovendien tientallen keren herhaald dient te worden, telkens met een ander masker.

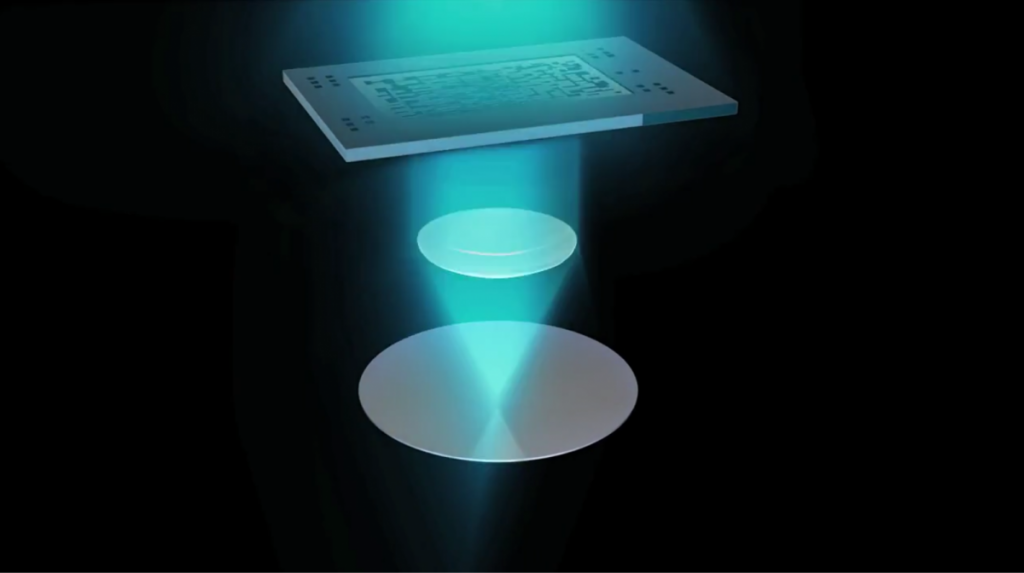

Een ASML-machine moet de wafers precies positioneren, zodat ze op exact de juiste plaats belicht worden. Dat belichten gebeurt met een bewegende lichtstraal die over het masker gaat, vergelijkbaar met de manier waarop een scanner scant. Het licht passeert vervolgens een serie lenzen die de projectie verkleinen, waarna een hele batterij extra lenzen de afwijkingen van de vorige lenzen moet compenseren. Iedere lens, hoe goed ook, heeft een minieme afwijking en op de nanometerschaal moet die zo goed mogelijk worden weggewerkt: het resultaat: een bijna komisch grote lenzenconstructie van enkele honderden kilo’s zwaar, ingepakt in een koelende behuizing.

Warmte vervormt, dus moet de lens op een exacte temperatuur blijven. ASML werkt samen met Zeiss voor de bouw van de lenzen, die een van de duurste onderdelen van het systeem vormen. Met een prijskaartje van enkele miljoenen voor één onderdeel begrijp je meteen waarom jij de afgewerkte machine niet kan betalen.

Licht als potlood

De minuscule schaal waarop alles gebeurt, heeft gevolgen voor het licht dat de machines gebruiken. Is lithografie het potlood waarmee Intel en consorten hun chips tekenen, dan is het licht de potloodpunt. “Licht is een groot woord voor wat we gebruiken in onze machines”, vindt Vreeker. “In moderne machines gebruiken we Diep UV-licht en dat is helemaal niet zichtbaar voor het menselijke oog.” De golflenges van het gebruikte Diep UV-licht, liggen in de grote-orde van tientallen nanometers. Het menselijk oog ziet licht met golflengtes tussen de 400 en de 700 nanometer. Intel gebruikt machines met diep UV-licht voor de fabricage van zijn nieuwste chips. De wet van Moore dicteert dat transistors steeds kleiner moeten worden, dus moet ook de potlootpunt kleiner.

“We werken momenteel aan machines die werken met extreem UV-licht”, vertelt Vreeker. “Dat ‘licht’ heeft golflengtes van minder dan 14 nanometer, wat voordelen maar ook technische uitdagingen met zich meebrengt.” ASML bouwde echter met succes de eerste generaties EUV-systemen. Er staan momenteel acht van dit soort machines in het veld. “ééntje staat hier bij imec”, vertelt professor Groeseneken met enige trots. De ontwikkeling van de machine illustreert de samenhang tussen de fabrikanten van de chips zoals Intel, de producenten van de machines zoals ASML en de high-tech onderzoeksinstituten zoals imec.

imec en de fabrikanten

“Bij imec leren we de machines van ASML te gebruiken. Het onderzoek naar de ontwikkeling van nieuwe manieren om kleinere chips te maken, is tijdsintensief en duur.” Intel, maar ook Samsung en de andere fabrikanten, kloppen aan bij imec voor dat onderzoek. “Zij leggen bij wijze van spreken samen om ons onderzoek te financieren, waarna we de resultaten en technieken met hen delen.”

imec is wat dat betreft één van de grote namen in de industrie, met onderzoekcentra over de hele wereld en samenwerkingscontracten met alle grote klinkende namen, niet alleen Samsung, Intel en TSMC, maar ook GlobalFoundries, Qualcomm, Huawei, Micron en Toshiba, om er maar enkele te noemen.

Waarom toch die zoektocht naar steeds kleinere transistors? Je kan denken dat het om het volume gaat: meer transistors op één chip brengt uiteraard voordelen met zich mee, maar dat is niet de belangrijkste motivatie. Een nul verandert in een één binnenin een chip wanneer een bepaald spanningsniveau bereikt wordt. “Hoe kleiner de transistors, hoe sneller ze kunnen wisselen tussen één en nul.” Een kleinere transistor is per definitie een snellere transistor, met dank aan de natuurkunde.

| Inhoudsopgave | |

| Stap 1: De wafer | Stap 6: Ionen-bombardement |

| Stap 2: Eerste laagje | Stap 7: Verbindingen |

| Stap 3: Lithografie | Het gereedschap |

| Stap 4: Etsen | De afwerking |

| Stap 5: De poort |

De afwerking

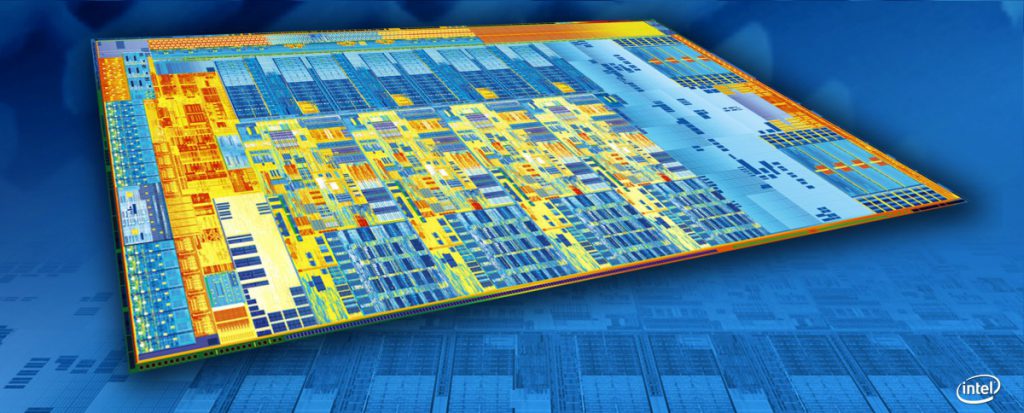

Het proces is ingewikkeld en de machines worden steeds complexer, maar het eindresultaat is telkens hetzelfde: een ronde wafer met daarop enkele tientallen chips. Langs de onderkant is de wafer gewoon grijs: het originele siliciumkristal is daar volledig intact. Bovenaan glinstert de chip in verschillende kleuren. Dat is het resultaat van de verschillende koperen interconnects, die het licht op unieke manieren breken. Het hele proces, van wafer tot chip, duurt al snel enkele weken. Intel communiceert niet meer over de exacte snelheid van het productieproces, maar laat ons weten dat de wafer op minder dan zes weken door de fab passeert.

Een fijne diamantzaag verdeelt de wafer nu in individuele chips. Die worden vervolgens grondig getest. Iedere chip op eenzelfde wafer is gemaakt met hetzelfde ontwerp, maar dat wil niet zeggen dat ze identiek zijn. Tijdens het productieproces wordt materiaal telkens van het midden uit verspreid over de wafer. Groeseneken: “Daarom is die ook rond, terwijl de chips zelf rechthoekig zijn.” Ondanks de geweldige nauwkeurigheid van het hele proces is enige variatie onvermijdelijk. Dat resulteert in chips met een identiek design, maar een licht verschillende kloksnelheid. Intel test de chips, bepaalt de kloksnelheid die ze consequent halen (met een gezonde marge) en geeft ze een verschillend typenummer. De Intel Core i5-4460 en de Intel Core i5-4440S bijvoorbeeld, hebben een identiek ontwerp maar de kloksnelheid van die laatste ligt net iets lager. Beide chips zijn dus afkomstig van dezelfde wafers en hebben exact dezelfde stappen doorlopen.

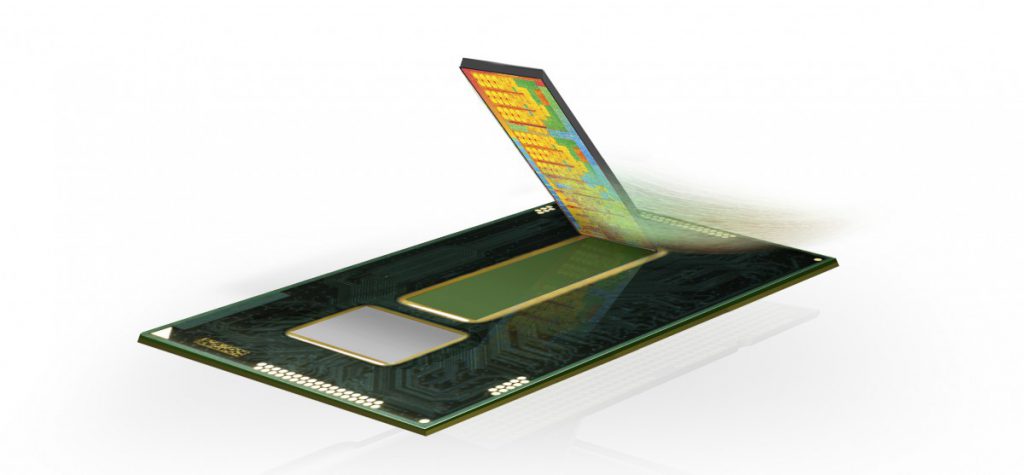

Substraat

Na het testen wordt de chip ‘geflipt’. De glinsterende bovenkant komt, wanneer het over een processorchip gaat, in een substraat terecht. Dat substraat heeft langs de onderzijde een heleboel gouden verbindingen. Die verbindingen sluiten rechtstreeks aan op de bovenste interconnects van de chip. Je klikt de chip met de pinnen van het substraat naar omlaag in het moederbord, zodat de processor kan praten met je systeem. Langs de andere kant komt een hittegeleidend metaal, dat tegen het silicium van de chip plakt, zonder ruimte voor lucht. Daarlangs verdwijnt de hitte, meestal via een koeler die jij of een computerfabrikant tegen de chip duwen.

Niet alleen processors worden op een dergelijke manier gemaakt: alle computerchips volgen een gelijkaardig productieproces. Het design (de maskers en de opeenvolging van stappen) is anders, maar de essentie blijft hetzelfde. In het geval van een grafische kaart komt de chip dan niet in een substraat terecht, maar in een gpu.

Altijd hetzelfde

Computers en chips worden steeds krachtiger, maar het principe blijft sinds de uitvinding van de CMOS hetzelfde. Het proces begint met een wafer, laag na laag krijgt die wafer nieuw materiaal, gedeponeerd in door lithografie bepaalde patronen. Onderaan zit de transistor, daarboven liggen de interconnects die de transistors met elkaar verbinden. Zo komen logische schakelingen tot stand, zoals AND, OR, NAND en NOR-schakelingen, of registers zoals flip flops. Die maken de chip slim, zodat hij code kan uitvoeren. Op die elementaire code wordt software gebouwd, zodat ook jij de chip kan gebruiken.